### PAMS Technical Documentation RAE-2 Series transceiver

## Chapter 3 -Transceiver BS8 BS8 RF Block

**Technical Documentation**

#### **AMENDMENT RECORD SHEET**

| Amendment<br>Number | Date  | Inserted By | Comments |

|---------------------|-------|-------------|----------|

|                     | 02/99 |             | Original |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

|                     |       |             |          |

Page 3 – 2 Original 02/99

#### **CONTENTS - RF**

|                                   | Page No |

|-----------------------------------|---------|

| Introduction                      | 3 – 5   |

| Technical summary                 | 3 – 5   |

| RF Characteristics                | 3 – 5   |

| Transmitter Characteristics       | 3 – 6   |

| Output power                      | 3 – 6   |

| Receiver characteristics          | 3 – 7   |

| DC characteristics                | 3 – 8   |

| Regulators                        | 3 – 8   |

| Power distribution diagram        | 3 – 8   |

| Functional descriptions           | 3 – 10  |

| Normal and extreme voltages       | 3 – 10  |

| RF block diagram                  | 3 – 10  |

| Frequency synthesizers            | 3 – 12  |

| Receiver                          | 3 – 13  |

| Transmitter                       | 3 - 14  |

| AGC strategy                      | 3 – 16  |

| AFC function                      | 3 – 17  |

| RF block requirements             | 3 – 18  |

| Duplex filter                     | 3 – 18  |

| Receiver blocks                   | 3 – 18  |

| LNA in CRFU_1a                    | 3 – 18  |

| RX interstage filter              | 3 – 19  |

| 1st mixer in CRFU_1a              | 3 – 19  |

| 1st IF–filter                     | 3 - 20  |

| AGC-stage and 2nd mixer in SUMMA  | 3 - 20  |

| 2nd IF Filter                     | 3 – 21  |

| Buffer in SUMMA for 2nd IF        | 3 – 21  |

| Transmitter blocks                | 3 – 21  |

| IQ-modulator and TX-AGC in SUMMA  | 3 – 21  |

| 116 MHz LC TX IF-filter           | 3 – 22  |

| Upconversion mixer and in CRFU_1a | 3 – 23  |

| TX interstage filter              | 3 – 23  |

| Power amplifier MMIC              | 3 – 24  |

| Directional coupler               | 3 – 25  |

| Power detector                    | 3 - 25  |

| Power control section in SUMMA    | 3 – 26  |

| Synthesizers blocks               | 3 – 27  |

| VCTCXO, reference oscillator      | 3 – 27  |

| VHF PLL in SUMMA                  | 3 – 28  |

| VHF VCO and low pass filter       | 3 – 28  |

| BS8_RF                            | Technical Documentation |  |

|-----------------------------------|-------------------------|--|

|                                   |                         |  |

| UHF PLL                           | 3 – 29                  |  |

| UHF VCO module                    | 3 – 30                  |  |

| UHF local signal input in CRFU_1a | 3 – 31                  |  |

| RF/BB/DSP Interface               | 3 – 31                  |  |

| Interface Signal Characteristics  | 3 – 31                  |  |

| Data Interface and Timing         | 3 – 32                  |  |

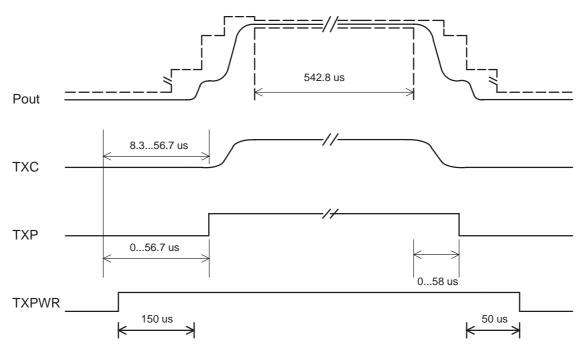

| Transmit Power Timing             | 3 – 34                  |  |

| SUMMA and Synthesizer Control     | 3 – 35                  |  |

| Registers                         | 3 – 35                  |  |

| PLL Control Word Format           | 3 – 35                  |  |

| Control Register                  | 3 – 35                  |  |

| Synthesizer clocking              | 3 – 36                  |  |

| GSM Division ratios               | 3 – 36                  |  |

| Clocking scheme                   | 3 – 36                  |  |

| SUMMA and Synthesizer Control     |                         |  |

| List of abbreviations             | 3 – 36                  |  |

Page 3 – 4 Original 02/99

#### Introduction

This document defines the RF-module of the RAE-2 GSM-"engine". This section contains electrical specifications, functional descriptions, block diagrams etc.

#### **Technical summary**

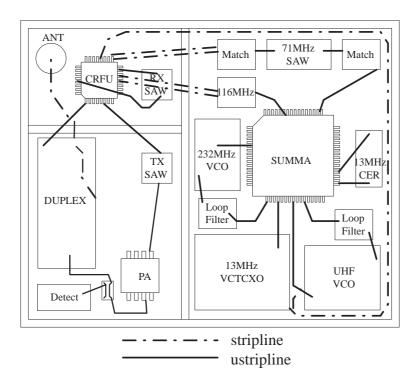

The RF in the RAE-2 GSM is based on the architecture used in DCT 3.

The RAE–2 RF Engine (figure below) is a single side design, on the A–side, with all components located under the PDA unit. Shielding comprises three shielding cans with removable lids. The maximum building height for the RF Engine is 2 mm.

#### **RF Characteristics**

Table 1. Main RF characteristics

| Item                     | Values      |  |  |

|--------------------------|-------------|--|--|

| Receive frequency range  | 935 960 MHz |  |  |

| Transmit frequency range | 890 915 MHz |  |  |

| Duplex spacing           | 45 MHz      |  |  |

| Channel spacing          | 200 kHz     |  |  |

**Technical Documentation**

Table 1. Main RF characteristics (continued)

| Item                   | Values |

|------------------------|--------|

| Number of RF channels  | 124    |

| Power class            | 4      |

| Number of power levels | 15     |

Note 1 : Standard of primary GSM 900 Band, P - GSM

890 – 915 MHz : Mobile transmit, Downlink 935 – 960 MHz : Mobile receive, Uplink

#### **Transmitter Characteristics**

| Item                                       | Values                             |  |  |

|--------------------------------------------|------------------------------------|--|--|

| Туре                                       | Upconversion, nonlinear, FDMA/TDMA |  |  |

| Intermediate frequency ( phase modulated ) | 116 MHz                            |  |  |

| LO frequency range                         | 1006 1031 MHz                      |  |  |

| Output power                               | 2 W peak ( 33 dBm )                |  |  |

| Power control range                        | min. 5 33 dBm                      |  |  |

| Maximum phase error ( RMS/peak )           | max 5 deg./20 deg. peak            |  |  |

#### **Output power**

| Parameter                                   | Min. | Тур. | Max.               | Unit / Notes                          |

|---------------------------------------------|------|------|--------------------|---------------------------------------|

| Max. output power                           |      | 33.0 |                    | dBm                                   |

| Max. output power tolerance (power level 5) |      |      | +/- 2.0<br>+/- 2.5 | dB, normal cond.<br>dB, extreme cond. |

| Output power tolerance / power levels 615   |      |      | +/- 3.0<br>+/- 4.0 | dB, normal cond.<br>dB, extreme cond. |

| Output power tolerance / power levels 1619  |      |      | +/- 5.0<br>+/- 6.0 | dB, normal cond.<br>dB, extreme cond. |

| Output power control step size              | 0.5  | 2.0  | 3.5                | dB                                    |

Note 1 : Output power refers to the measure of power when averaged over the useful part of the burst. Power levels are measured at the antenna connector.

Note 2: Interval between power steps shall be 2 +/-1.5 dB

Page 3 – 6 Original 02/99

#### **Receiver characteristics**

| Item                                                           | Values                                                                                             |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Туре                                                           | Linear, FDMA/TDMA                                                                                  |

| IF frequencies                                                 | 1st 71 MHz, 2nd 13 MHz                                                                             |

| LO frequencies                                                 | 1st LO 1006 1031 MHz, 2nd LO 58 MHz                                                                |

| Typical 1 dB bandwidth                                         | +/- 90 kHz                                                                                         |

| Sensitivity                                                    | min. – 102 dBm , S/N >8 dB                                                                         |

| Total typical receiver voltage gain ( from antenna to RX ADC ) | 73 dB                                                                                              |

| Receiver output level ( RF level –95 dBm )                     | 50 mVpp ( typical balanced signal level of 13 MHz IF in RF BB interface = input level to RX ADCs ) |

| Typical AGC range (dynamic range –93dB)                        | −17 +40 dB                                                                                         |

| Accurate AGC control range                                     | 57 dB                                                                                              |

| Typical AGC step in LNA                                        | –15 dB                                                                                             |

| Usable input dynamic range                                     | −102 −10 dBm                                                                                       |

| RSSI dynamic range                                             | −110 −48 dBm                                                                                       |

| AGC relative accuracy on channel ( accurate range )            | +/- 0.8 dB                                                                                         |

| Compensated gain variation in receiving band                   | +/- 1.0 dB                                                                                         |

RAE-2 PAMS

BS8\_RF

**Technical Documentation**

#### **DC** characteristics

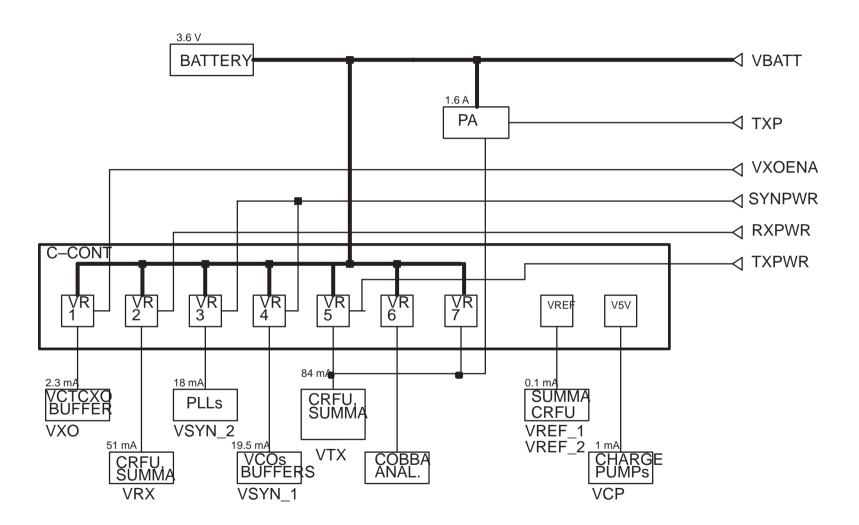

#### Regulators

Transceiver has got a multi function power management IC, which contains among other functions, also 7 pcs of 2.8 V regulators. All regulators can be controlled individually with 2.8 V logic directly or through control register. In GSM direct controls are used to get fast switching, because regulators are used to enable RF–functions.

Use of the regulators can be seen in the power distribution diagram.

CCONT also provides 1.5 V reference voltage for SUMMA and CRFU1a ( and for DACs and ADCs in COBBA too ).

All control signals are coming from MAD and they are 2.8 V logic signals..

Page 3 – 8 Original 02/99

PAMS

# Power distribution diagram

RAE-2 PAMS

BS8\_RF

**Technical Documentation**

#### **Functional descriptions**

#### RF block diagram

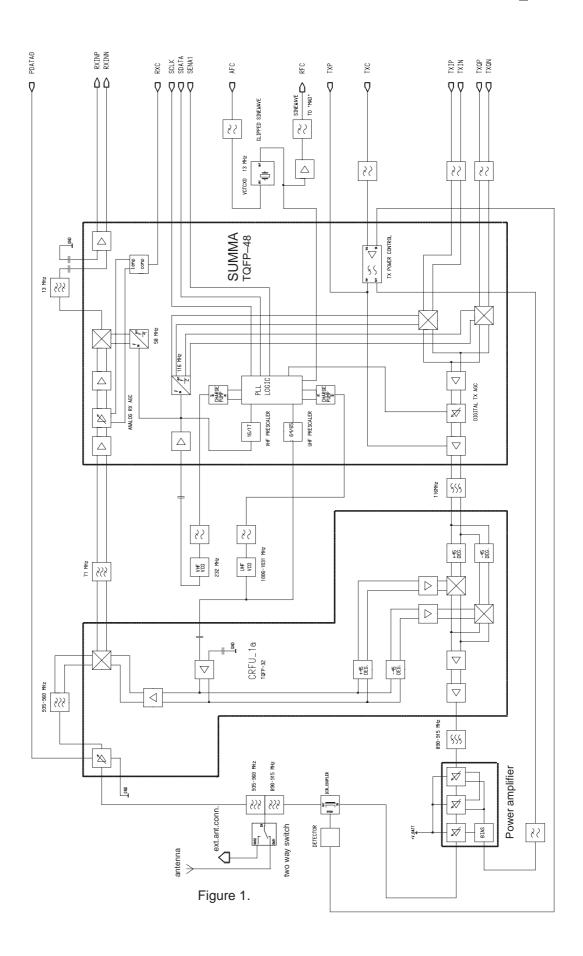

The RF block comprises a conventional dual conversion receiver and the transmitter features an up–conversion mixer for the final TX–frequency.

The architecture contains three ICs. Most of the functions are horizontally and vertically integrated. UHF functions except power amplifier and VCO are integrated into CRFU\_1a, which is a BiCMOS-circuit suitable for LNA- and mixer-function. Most of the functions are in SUMMA, which also is a BiCMOS-circuit. SUMMA is a IF-circuit including IQ-modulator and PLLs for VHF- and UHF-synthesizers.

Power amplifier is also an ASIC, it is a so called MMIC (monolithic microwave integrated circuit). It has got three amplifier stages including input and interstage matchings. Output matching network is external. Also TX gain control is integrated into this chip.

See block diagram next page

Page 3 – 10 Original 02/99

Technical Documentation

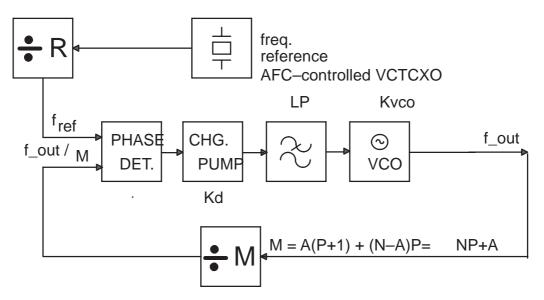

#### Frequency synthesizers

Both VCOs are locked with PLLs into stable frequency source, which is a VCTCXO-module (voltage controlled temperature compensated crystal oscillator). The VCTCXO is running at 13 MHz. Temperature effect is controlled with AFC (automatic frequency control) voltage, the VCTCXO is locked into the frequency of the base station. AFC is generated by baseband with a 11 bit conventional DAC in COBBA.

The UHF PLL is located in the SUMMA. There is 64/65 (P/P+1) prescaler, N– and A–divider, reference divider, phase detector and charge pump for the external loop filter.

The UHF local signal is generated by a VCO-module ( VCO = voltage controlled oscillator ) and sample of frequency of VCO is fed to prescaler. The prescaler is a dual modulus divider. The output of the prescaler is fed to the N- and A-dividers, which produce the input to phase detector.

The phase detector compares this signal to reference signal, which is divided with reference divider from VCTCXO output. Output of the phase detector is connected into charge pump, which charges or discharges integrator capacitor in the loop filter depending on the phase of the measured frequency compared to reference frequency.

The loop filter filters out the pulses and generates the DC to control the frequency of UHF–VCO. The loop filter defines step response of the PLL (settling time) and effects to stability of the loop, that's why integrator capacitor has got a resistor for phase compensation.

The other filter components are for sideband rejection. Dividers are controlled via serial bus. SDATA is for data, SCLK is serial clock for the bus and SENA1 is a latch enable, which stores new data into dividers. The UHF–synthesizer is the channel synthesizer, so the channel spacing is 200 kHz. 200 kHz is the reference frequency for the phase detector.

Page 3 – 12 Original 02/99

VHF PLL is also located into SUMMA. It comprises a 16/17 ( P/P+1 ) dual modulus prescaler, N— and A—dividers, reference divider, phase detector and charge pump for the loop filter. The VHF local signal is generated with a discrete VCO—circuit. The VHF PLL works in the same way as UHF—PLL. The VHF—PLL is locked on fixed frequency, so higher reference frequency is used to decrease phase noise.

#### Receiver

Receiver is a dual conversion linear receiver.

The received RF-signal from the antenna is fed via the duplex filter to LNA (low noise amplifier) in CRFU\_1a. Active parts (RF-transistor and biasing and AGC-step circuitry) are integrated into this chip. Input and output matching networks are external.

Gain selection is carried out with PDATA0 control. Gain step in LNA is activated when the RF-level in the antenna is about -45 dBm.

After the LNA amplified signal ( with low noise level ) is fed to bandpass filter, which is a SAW-filter ( SAW, surface acoustic wave ).

This bandpass filtered signal is then mixed down to 71 MHz, which is the first intermediate frequency. The 1st mixer is located into CRFU\_1a ASIC. This integrated mixer is a double balanced Gilbert cell. All active parts and biasing are integrated and matching components are external. Because this is an axtive mixer it also amplifies IF–frequency. Also local signal buffering is integrated and upper side injection is used. First local signal is generated by the UHF–synthesizer.

The first IF–signal is then bandpass filtered with a selective SAW–filter. From the mixer output to the IF–circuit input the signal path is balanced. The IF–filter provides selectivity for channels greater than +/–200 kHz. Also it attenuates image frequency of the second mixer and intermodulat-

Technical Documentation

ing signals. Selectivity is required in this place, because of needed linearity and adjacent channel interferers will be on too high signal level for the stages following.

The next stage in the receiver chain is AGC-amplifier. It is integrated into SUMMA-ASIC. The AGC has got analog gain control. The control voltage for the AGC is generated with DA-converter in COBBA in baseband. AGC-stage provides accurate gain control range ( min. 57 dB ) for the receiver.

After the AGC there is the second mixer, which generates the second intermediate frequency, 13 MHz. The local signal is generated in SUMMA by dividing VHF–synthesizer output ( 232 MHz ) by four, so the 2nd LO–frequency is 58 MHz.

The 2nd IF–filter is a ceramic bandpass filter at 13 MHz. It attenuates adjacent channels, except for +/– 200 kHz there is not much attenuation. Those +/– 200 kHz interferers are filtered digitally by the baseband. So the RX DACs are so good, that there is enough dynamic range for the faded 200 kHz interferer. Also the whole RX has to be able to handle signal levels in a linear way

After the 13 MHz filter there is a buffer for the IF–signal, which also converts and amplifies single ended signal from filter to balanced signal for the buffer and AD–converters in COBBA. Buffer in SUMMA has got voltage gain of 36dB and buffer gain setting in COBBA is 0 dB. It is possible to set gainstep (9.5 dB) into COBBA via control bus, if needed..

#### **Transmitter**

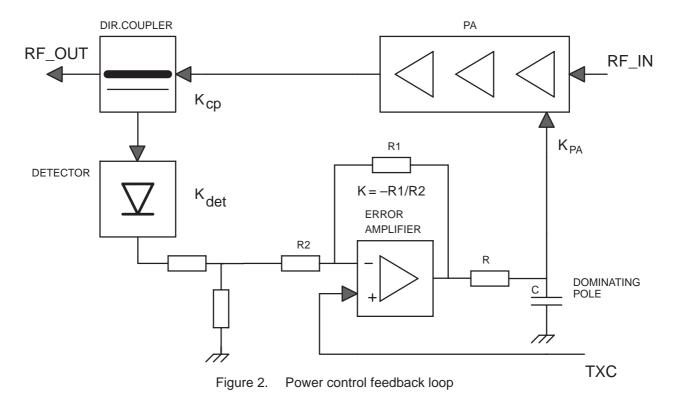

The transmitter chain consists of IQ-modulator, upconversion mixer, power amplifier and there is a power control loop.

I– and Q–signals are generated by baseband in COBBA–ASIC. After post filtering (RC–network) they are fed into IQ–modulator in SUMMA. It generates modulated TX IF–frequency, which is VHF–synthesizer output divided by two, that is 116 MHz. The TX–amplifier in SUMMA has two selectable gain levels. Output is set to maximum via control register of SUMMA. After SUMMA there is a bandpass LC–filter for noise and harmonic filtering before the signal is fed for upconversion into final TX–frequency in CRFU\_1a.

Upconversion mixer in CRFU\_1a is a so called image reject mixer. It attenuates the unwanted sideband in the upconverter output. The mixer itself is a double balanced Gilbert cell. The phase shifters required for image rejection are also integrated. The local signal needed in upconversion is generated by the UHF—synthesizer, but buffers for the mixer are integrated into CRFU\_1a.

The output of the upconverter is buffered and matching network makes a single ended 50 ohm impedance.

The next stage is a TX interstage filter, which attenuates the unwanted signals from the upconverter, mainly LO-leakage and image frequency

Page 3 – 14 Original 02/99

from the upconverter. Also it attenuates the wideband noise. This bandpass filter is a SAW-filter.

The final amplification is carried out by the third IC, the power amplifier which is a MMIC. It features a 50 ohm input, output requires an external matching network. The MMIC comprises three amplifier stages and interstage matchings. Also included is a gain control, which is controlled with a power control loop. The PA features over 35 dB power gain and it is able to produce 2.5 W into output with 0 dBm input level. The gain control range is over 35 dB to get desired power levels and power ramping up and down.

The harmonics generated by the nonlinear PA (class AB) are filtered out with the matching network and lowpass/bandstop filtering in the duplexer. Bandstop is required because of wideband noise located on RX–band.

Power control circuitry consists of a power detector in the PA output and an error amplifier in SUMMA. There is a directional coupler connected between the PA-output and the duplex filter. It takes a sample from the forward going power with certain ratio. This signal is rectified in a schott-ky-diode and it produces a DC-signal signal after filtering. This peak-detector is linear on absolute scale, except it saturates on very low and high power levels – it produces a S-shape curve.

This detected voltage is compared in the error–amplifier in SUMMA to TXC–voltage, which is generated by DA–converter in COBBA. Because also gain control characteristics in PA are linear in absolute scale, control loop defines a voltage loop, when closed. The closed loop tracks the TXC–voltage quite linearly.

The TXC has got a raised cosine form ( cos<sup>4</sup> – function ), which reduces switching transients, when pulsing power up and down. Because dynamic range of the detector is not wide enough to control the power ( actually RF output voltage ) over the whole range, there is a control named TXP to work under detected levels. Burst is enabled and set to rise with the TXP until the output level is high enough, that feedback loop works. The loop controls the output via the control pin in the PA MMIC to the desired output level and burst has got the waveform of TXC–ramps. Because feedback loops could be unstable, this loop is compensated with a dominating pole. This pole decreases gain on higher frequencies to get phase margins high enough.

**Technical Documentation**

#### **AGC** strategy

The AGC-amplifier is used to maintain output level of the receiver almost constant.

AGC has to be set before each received burst, this is called pre-monitoring. The receiver is switched on before the burst begins, the DSP measures received signal level and adjusts RXC, which controls RX AGC-amplifier or it switches off the LNA with PDATA0 control line. This pre-monitoring is done in three phases and this sets the settling times for RX AGC. Pre-monitoring is required because of linear receiver, received signal must be in full swing, no clipping is allowed and because DSP doesn't know, what is the level going to be in next burst.

There is at least 60 dB accurate gain control (continuous, analog) and one digital step in LNA. It is typically about 30...35 dB.

RSSI must be measured on range –48...–110 dBm. After –48 dBm level MS reports to base station the same reading.

Because of RSSI–requirements, gain step in LNA is used roughly on -45 dBm RF–level and up to -10 dBm input RF–level accurate AGC is used to set RX output level. LNA is ON ( PDATA0 = "0" ) below -47 dBm. from -47 dBm down to -95 dBm

This accurate AGC in SUMMA is used to adjust the gain to desired value. RSSI–function is in DSP, but it works out received signal level by measuring RX IQ–level after all selectivity filtering ( meaning IF–filters,  $\Sigma\Delta\pm$ converter and FIR–filter in DSP). So 50 dB accurate AGC dynamic range is

Page 3 – 16 Original 02/99

required. Remaining 10 dB is for gain variations in RX-chain (for calibration)

Below –95 dBm RF–levels, output level of the receiver drops dB by dB. At –95 dBm level output of the receiver gives 50 mVpp. This is the target value for DSP. Below this it drops down to ca. 9 mVpp @ –110 dBm RF–level.

This strategy is chosen because we have to roll off the AGC in PLUSSA early enough, that it won't saturate in selectivity tests. Also we can't start too early, then we will sacrifice the signal to noise ratio and it would require more accurate AGC dynamic range. 50 mVpp target level is set, because RX–DAC will saturate at 1.4 Vpp. This over 28 dB headroom is required to have margin for +/- 200 kHz faded adjacent channel (ca. 19 dB) and extra 9 dB for pre-monitoring.

Production calibration is done with two RF-levels, LNA gain step is not calibrated. The gain changes in the receiver are taken off from the dynamic range of accurate AGC. Variable gain stage in SUMMA is designed in a way, that it is capable of compensating itself, there is good enough margin in AGC.

#### **AFC** function

AFC is used to lock the transceivers clock to the frequency of the base station.

AFC-voltage is generated in the COBBA with a 11 bit AD-converter. There is a RC-filter in AFC control line to reduce the noise from the converter. Settling time requirement for the RC-network comes from signalling, how often PSW (pure sine wave) slots occur. They are repeated after 10 frames, meaning that there is PSW in every 46 ms.

AFC tracks the base station frequency continuously, so the transceiver has got a stable frequency, because changes in the VCTCXO-output don't occur so fast ( temperature ).

Settling time requirement comes also from the start up—time allowed. When transceiver is in sleep mode and "wakes" up to receive mode, there is only about 5 ms for the AFC—voltage to settle. When the first burst comes in system clock has to be settled into +/— 0.1 ppm frequency accuracy. Settling time requirement comes also from the start up—time allowed. When transceiver is in sleep mode and "wakes" up to receive mode, there is only about 5 ms for the AFC—voltage to settle. When the first burst comes in system clock has to be settled into +/— 0.1 ppm frequency accuracy.

The VCTCXO—module requires also 5 ms to settle into final frequency. Amplitude rises into full swing in 1 ... 3 ms, but frequency settling time is longer so this oscillator must be powered up early enough.

#### **RF block requirements**

#### **Duplex filter**

| Parameter                    | Transmit section                                  |      | Receive                                      | unit |        |

|------------------------------|---------------------------------------------------|------|----------------------------------------------|------|--------|

| Center frequency, ftx,frx    | ftx: 902.5                                        |      | frx : 947.5                                  | MHz  |        |

| BW ( bandwidth ) at passband | +/- 12.5                                          |      | +/- 12.5                                     | MHz  |        |

| Maximum insertion loss at BW | 1.6 ( at +25 deg. C )<br>1.9 ( at -20+85 deg. C ) |      | 3.2 (at +25 deg. C)<br>3.7 (at -20+85deg. C) |      | dB     |

| Ripple at BW, peak to peak   | 1.1                                               |      | 1.5                                          |      | dB     |

| Terminating impedance        | 50                                                |      | 50                                           |      | ohms   |

| Maximum VSWR                 | 2.2                                               |      | 1.8                                          |      |        |

| Minimum attenuations         | Freq.range                                        | Att. | Freq.range                                   | Att. |        |

|                              | 925935                                            | 3    | 3200                                         | 30   | MHz/dB |

|                              | 935960                                            | 15   | 200500                                       | 16   | MHz/dB |

|                              | 17801830                                          | 28   | 500890                                       | 25   | MHz/dB |

|                              | 26702745                                          | 35   | 890915                                       | 26   | MHz/dB |

|                              |                                                   |      | 9801000                                      | 21   | MHz/dB |

|                              |                                                   |      | 10001050                                     | 23   | MHz/dB |

|                              |                                                   |      | 14001500                                     | 35   | MHz/dB |

| Permissible input pow-<br>er | 4.0 AVG (12.5% duty cyclr)                        |      |                                              | W    |        |

Part no: NMP code 4512075

#### **Receiver blocks**

#### LNA in CRFU\_1a

| Parameter                    | Min.      | Тур. | Max.  | Unit/Notes    |

|------------------------------|-----------|------|-------|---------------|

| Frequency band               | 935 – 960 |      |       | MHz           |

| Supply voltage               | 2.7       | 2.8  | 2.855 | V             |

| Current consumption          |           |      | 8     | mA            |

| Insertion gain               | 17.5      | 18.5 | 19.5  | dB            |

| Noise figure                 |           | 1.7  | 2.2   | dB,PDATA0=H   |

| Input 1 dB compression point | -19       |      |       | dBm, PDATA0=H |

| Reverse isolation            | 15        |      |       | dB            |

| Input VSWR                   |           |      | 2     |               |

Page 3 – 18 Original 02/99

| Parameter                  | Min. | Тур. | Max. | Unit/Notes         |

|----------------------------|------|------|------|--------------------|

| Output VSWR                |      |      | 2    |                    |

| Gain reduction             | 30   |      | 35   | dB,room temp.      |

| Step accuracy              | -2   |      | +2   | dB,over temp.range |

| Noise figure, when PDATA=0 |      | 20   |      | dB                 |

#### **RX** interstage filter

| Parameter                | Min.              | Тур.      | Max. | Unit |

|--------------------------|-------------------|-----------|------|------|

| Passband                 | 935 – 960         |           |      | MHz  |

| Insertion loss           |                   |           | 3.3  | dB   |

| Ripple in passband       |                   |           | 1.3  | dB   |

| Attenuation DC890 MHz    | 45                |           |      | dB   |

| Attenuation 890915 MHz   | 25                |           |      | dB   |

| Attenuation 9801030 MHz  | 25                |           |      | dB   |

| Attenuation 10253000 MHz | 35                |           |      | dB   |

| Terminating impedance    | UNBALANO<br>50/50 | CED-BALAN | ICED | ohm  |

| VSWR                     |                   |           | 2.0  |      |

| Maximum drive level      |                   |           | +15  | dBm  |

Part no: NMP code 4511049

#### 1st mixer in CRFU\_1a

| Parameter                     | Min. | Typ./<br>Nom. | Max. | Unit/Notes |

|-------------------------------|------|---------------|------|------------|

| Supply voltage                | 2.7  | 2.8           | 2.85 | V          |

| Current consumption           |      | 9             |      | mA         |

| RX frequency range            | 935  |               | 960  | MHz        |

| LO frequency range            | 1006 |               | 1031 | MHz        |

| IF frequency                  |      | 71            |      | MHz        |

| Insertion gain                | 9    |               | 12   | dB         |

| NF, SSB                       |      |               | 11.5 | dB         |

| IIP3                          | 0    |               |      | dBm        |

| 1 dB input compression point  | -10  |               |      | dBm        |

| IF/2 spurious level           | -30  |               |      | dBm, *     |

| LO power level in RF-port     |      |               | -25  | dBm        |

| Input VSWR                    |      |               | 2    |            |

| Output resistance (balanced)  | 10 k |               |      | ohm        |

| Output capacitance (balanced) |      | 1.2           |      | pF         |

#### 1st IF-filter

| Parameter                                                                                                                      | min.             | typ.                       | max.                                     | unit                     |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|------------------------------------------|--------------------------|

| Operating temperature range                                                                                                    | -20              |                            | +75                                      | deg.C                    |

| Center frequency, fo                                                                                                           |                  | 71                         |                                          | MHz                      |

| Maximum ins. loss at 1dBBW                                                                                                     |                  |                            | 11                                       | dB                       |

| Group delay ripple at +/-90 kHz BW                                                                                             |                  |                            | 1.3                                      | us pp                    |

| Bandwidths relative to 71 MHz 1 dB bandwidth 3 dB bandwidth 5 dB bandwidth 22 dB bandwidth 30 dB bandwidth 40 dB bandwidth     | +/- 70<br>+/-120 |                            | +/- 230<br>+/- 350<br>+/- 550<br>+/- 700 | kHz                      |

| Spurious rejection, fo +/- 26 MHz                                                                                              | 65               |                            |                                          | dB, *                    |

| Terminating impedance (balanced) resistance input resistance output capacitance (parallel) input capacitance (parallel) output |                  | 1.1<br>1.2<br>15.6<br>10.6 |                                          | kohm<br>kohm<br>pF<br>pF |

Matching network included. NMP part no. 4510137

#### AGC-stage and 2nd mixer in SUMMA

| Parameter                                    | Min.    | Тур.  | Max.    | Unit/Notes |

|----------------------------------------------|---------|-------|---------|------------|

| Supply voltage                               | 2.7     | 2.8   | 2.85    | V          |

| Current consumption                          |         | 27    | 32      | mA         |

| Input frequency range                        | 45      |       | 120     | MHz        |

| 2nd IF frequency range                       | 0.4     |       | 17      | MHz        |

| Total noise figure, SSB, max. gain           |         |       | 15      | dB,        |

| Total noise figure, SSB, min. gain           |         |       | 65      | dB,        |

| Max. voltage gain                            | 40      |       |         | dB         |

| Min. voltage gain                            |         |       | -20     | dB         |

| Control voltage for min. gain                |         | 0.5   |         | V          |

| Control voltage for max. gain                |         | 1.4   |         | V          |

| Output 1 dB compression point @ max. gain    | 800     |       |         | mVpp       |

| Input 1 dB compresion point<br>@ min. gain   | 80      |       |         | mVpp       |

| IF input impedance (balanced)                | 2.4/tbd | 3.8/2 | 5.6/tbd | kohm/pF    |

| 2nd mixer output impedance ( single output ) |         |       | 100     | ohm        |

Page 3 – 20 Original 02/99

PAMS RAE-2

**Technical Documentation**

BS8\_RF

#### 2nd IF Filter

| Parameter                                                                                 | min.           | typ. | max. | unit |

|-------------------------------------------------------------------------------------------|----------------|------|------|------|

| Center frequency, fo                                                                      |                | 13   |      | MHz  |

| 1 dB bandwidth, 1dBBW<br>( relative to 13 MHz )                                           | +/- 90         |      |      | kHz  |

| Insertion loss                                                                            |                |      | 6.0  | dB   |

| Amplitude ripple at 1dBBW                                                                 |                |      | 1.0  | dB   |

| Group delay ripple at 1 dB<br>BW, peak to peak                                            |                |      | 1.5  | us   |

| Attenuations, relative to<br>13 MHz<br>fo +/- 400 kHz<br>fo +/- 600 kHz<br>fo +/- 800 kHz | 25<br>35<br>45 |      |      | dB   |

| Terminating impedance                                                                     | 313            | 330  | 347  | ohm  |

NMP part no. 4510009

#### **Buffer in SUMMA for 2nd IF**

| Parameter                                                | Min. | Тур.  | Max. | Unit    |

|----------------------------------------------------------|------|-------|------|---------|

| Input frequency range                                    | 0.4  |       | 17   | MHz     |

| Voltage gain ( single ended input and balanced output )  | 34   | 36    | 38   | dB      |

| 1 dB output compression point ( Rload=10 kohm balanced ) |      | 1.4   |      | Vpp     |

| Input impedance                                          |      | 3.3/4 |      | kohm/pF |

| Output impedance, balanced                               |      |       | 600  | ohm     |

#### **Transmitter blocks**

#### IQ-modulator and TX-AGC in SUMMA

| Parameter                                                                                      | Min.       | Тур.                 | Max.    | Unit         |

|------------------------------------------------------------------------------------------------|------------|----------------------|---------|--------------|

| Supply voltage                                                                                 | 2.7        | 2.8                  | 2.85    | V            |

| Current consumption                                                                            |            | 28                   | tbd.    | mA           |

|                                                                                                |            |                      |         |              |

| Modulator Inputs (I/Q)                                                                         | Minimum    | Typical /<br>Nominal | Maximum | Unit / Notes |

| Input bias current (balanced)                                                                  |            |                      | 100     | nA           |

| Input common mode voltage                                                                      |            | 0.8                  |         | V            |

| Input level (balanced)                                                                         |            |                      | 1.2     | Vpp          |

| Input frequency range                                                                          | 0          |                      | 300     | kHz          |

| Input resistance (balanced)                                                                    | tbd        |                      |         | kohms        |

| Input capacitance (balanced)                                                                   |            |                      | 2       | pF           |

| IQ-input phase balance total, temperature included                                             | -4         |                      | 4       | deg.         |

| IQ-input phase balance temperature effect                                                      | -2         |                      | 2       | deg.         |

| IQ-input amplitude balance total, temperature included                                         | -0.5       |                      | 0.5     | dB           |

| IQ-input amplitude balance temperature effect                                                  | -0.2       |                      | 0.2     | dB           |

| Modulator Output                                                                               | Minimum    | Typical /<br>Nominal | Maximum | Unit / Notes |

| Output frequency                                                                               | 85         |                      | 400     | MHz          |

| Output power, high (balanced, into 100 ohm) NOTE: Requires input level of 1.1 Vpp (difrential) | <b>-</b> 5 | -3                   |         | dBm          |

| Output power, low (balanced, into 100 ohm ) NOTE: Requires input level of 1.1 Vpp (diff.)      | -10        | -8                   |         | dBm          |

| Noise level in output                                                                          |            |                      | -145    | dBm/Hz avg.  |

| Total gain control range                                                                       | 35         |                      |         | dB           |

| Gain step                                                                                      |            | 5                    |         | dB           |

Page 3 – 22 Original 02/99

| Modulator Output                                                                                              | Minimum | Typical /<br>Nominal | Maximum        | Unit / Notes |

|---------------------------------------------------------------------------------------------------------------|---------|----------------------|----------------|--------------|

| Absolute gain accuracy                                                                                        | -2      |                      | +2             | dB           |

| Any gain step up/down set-<br>tling time                                                                      |         |                      | 10             | usec         |

| Output 3rd Order Intermodulation products, when both wanted signals are at the level of -12 dBm at the output |         |                      | <del>-35</del> | dB           |

#### 116 MHz LC TX IF-filter

| Parameter                                | Min. | Тур. | Max. | Unit |

|------------------------------------------|------|------|------|------|

| Center frequency                         |      | 116  |      | MHz  |

| Insertion loss @ 116 MHz                 |      |      | 3.7  | dB   |

| Relative attenuation @ +/- 10 MHz offset | 5    |      |      | dB   |

| Relative attenuation @ +/- 20 MHz offset | 8    |      |      | dB   |

| Relative attenuation @ 232<br>MHz        | 15   |      |      | dB   |

| Relative attenuation @ 348 MHz           | 20   |      |      | dB   |

| Relative attenuation @ 464–1000 MHz      | 25   |      |      | dB   |

| Input impedance, balanced                |      | 100  |      | ohm  |

| Output impedance, balanced               |      | 200  |      | ohm  |

#### Upconversion mixer and in CRFU\_1a

| Parameter                 | Min. | Тур.       | Max. | Unit |

|---------------------------|------|------------|------|------|

| Supply voltage            | 2.7  | 2.8        | 2.85 | V    |

| Supply current            |      |            | 50   | mA   |

| Input frequency           |      | 116        |      | MHz  |

| Input level               |      | <b>-</b> 5 | -8   | dBm  |

| Output frequency range    | 890  |            | 915  | MHz  |

| Output level              | +3   | +5         |      | dBm  |

| NF,SSB                    |      |            | 20   | dB   |

| LO-signal level in output |      |            | -29  | dBc  |

| Unwanted sideband level   |      |            | -15  | dBc  |

| fLO+/-2xIF spurious level |      |            | -40  | dBc  |

| 7x116 MHz spurious level  |      |            | -40  | dBc  |

| Parameter                                              | Min. | Тур.   | Max.        | Unit    |

|--------------------------------------------------------|------|--------|-------------|---------|

| 8x116 MHz spurious level                               |      |        | <b>-</b> 55 | dBc     |

| Input impedance (balanced)                             |      | 600//2 |             | ohm//pF |

| Output VSWR, ( with matching network and output balun) |      |        | 2           |         |

#### TX interstage filter

| Parameter                | Min.      | Тур. | Max. | Unit |

|--------------------------|-----------|------|------|------|

| Passband                 | 890 – 915 |      |      | MHz  |

| Insertion loss           |           |      | 3.8  | dB   |

| Ripple in passband       |           |      | 1.5  | dB   |

| Attenuation DC813 MHz    | 35        |      |      | dB   |

| Attenuation 925935 MHz   | 7         |      |      | dB   |

| Attenuation 935960 MHz   | 15        |      |      | dB   |

| Attenuation 10061031 MHz | 40        |      |      | dB   |

| Attenuation 11221147 MHz | 45        |      |      | dB   |

| Attenuation 17801830 MHz | 10        |      |      | dB   |

| Attenuation 26702745 MHz | 10        |      |      | dB   |

| Terminating impedance    |           | 50   |      | ohm  |

| VSWR                     |           |      | 2.5  |      |

| Maximum drive level      |           |      | +15  | dBm  |

NMP part no. 4511015

#### **Power amplifier MMIC**

| Parameter                                                    | Symbol | Test condition                                                                                               | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Operating freq. range                                        |        |                                                                                                              | 880  |      | 915  | MHz  |

| Supply voltage                                               | Vcc    |                                                                                                              | 3.0  | 3.5  | 5.0  | V    |

| Auxiliary supply voltage                                     | Vreg   |                                                                                                              | 2.7  | 2.8  | 2.9  | V    |

| Auxiliary supply current                                     | Ireg   |                                                                                                              |      |      | tdb. | mA   |

| Input power                                                  | Pin    | Pout=35.0 dBm, Vcc=3.5 V, Vpc=2.2 V,                                                                         | 0    | 2    | 5    | dBm  |

| Output power                                                 | Pout   | Pin= 0 dBm, Vcc=3.0 V,<br>Vpc=2.2 V, Tamb=+85 deg.C                                                          | 34.2 |      |      | dBm  |

| Gain control range<br>( overall dynamic<br>range)            |        | Vpc= 0.5 2.2 V                                                                                               | 45   |      |      | dB   |

| Gain control slope<br>( sensitivity at the linear<br>range ) | S      | Vpc1 @10 Vpeak output volt.<br>Vpc2 @0.5 Vpeak output volt.<br>S=((10-0.5)/(Vpc1-Vpc2))<br>V/V, Pin = 0+5dBm | 20   | tbd. | 40   | V/V  |

Page 3 – 24 Original 02/99

| Parameter                  | Symbol | Test condition                                                                                                                                                                      | Min                                                            | Тур       | Max    | Unit       |

|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|--------|------------|

| Isolation                  |        | Vcc=3.5 V, Vpc=0.2 V, Pin=0 dBm                                                                                                                                                     |                                                                |           | -40    | dB         |

| Carrier switching time     | tr, tf | Vcc=3.5 V, Pin=0 dBm<br>Vpc is a pulse from 0.2 to 2.2<br>V. Rise time up to -0.5 dB<br>from the final power. Fall time<br>vice versa.                                              |                                                                |           | 1      | us         |

| Total efficiency           | η      | Pin= 0 dBm , Pout= +34.3 dBm, Vcc=3.5 V, Tamb = + 25 deg. C                                                                                                                         | 50                                                             |           |        | %          |

| Control current            | lpc    | Pin= 0+5 dBm , Pout=<br>+34.8 dBm, Vcc=3.5 V                                                                                                                                        |                                                                |           | +/- 3  | mA<br>peak |

| Harmonics                  |        |                                                                                                                                                                                     |                                                                |           | -35    | dBc        |

| Input VSWR                 | VSWRi1 | Pin= 0+5 dBm , Pout=<br>+34.0 dBm, Vcc=3.5 V                                                                                                                                        |                                                                |           | 2:1    |            |

|                            | VSWRi2 | Pin= 0+5 dBm , Pout= +6.0 +32.0 dBm, Vcc=3.5 V Vpc adjusted for desired power levels                                                                                                |                                                                |           | 4:1    |            |

| Leakage current            | lleak  | Vcc=3.5 V, Vpc=0 V,<br>Vreg=0 V, no RF-drive                                                                                                                                        |                                                                |           | 10     | uA         |

| Intermodulation distorsion | IMD    | Pinwant= 0 dBm @ 915 MHz<br>Pinint = -50 dBm @ 905 MHz<br>Poutwant= +34.8 dBm<br>Vcc=3.5 V,<br>Poutint @905 MHz<br>Poutimd @925 MHz<br>IMD=Poutint - Poutimd,<br>Tamb = + 25 deg. C | 5                                                              |           |        | dB         |

| AM-PM conversion           | Кр     | Pin= -2.0 +5.0 dBm,<br>Pout= +6.0 +34.0 dBm<br>Vpc adjusted for desired out-<br>put power levels<br>Vcc=3.0 V                                                                       |                                                                |           | 3      | deg/dB     |

| Receive band noise power   | Pn     | Vcc=3.5 V , RBW=30kHz<br>Pout = +34.8 dBm, Freq.<br>band: 925960 MHz                                                                                                                |                                                                |           | -80    | dBm        |

| Stability                  |        | Pin= 0 dBm+/-3dBm,<br>Vcc=3.05.0 V,<br>Vpc=0 2.2 V<br>Load VSWR 12:1, all phases                                                                                                    | All spurious outputs more than 6 dB below desired signal hases |           | nan 65 |            |

| Load mismatch stress       |        | Pin= 0 dBm, Vcc=5.0 V,<br>Pout=Pmax<br>Load VSWR 20:1, all phases                                                                                                                   | No modu                                                        | ıle damaç | ge     |            |

#### **Directional coupler**

| Parameter                           | Min. | Тур. | Max. | Unit/Notes |

|-------------------------------------|------|------|------|------------|

| Frequency range                     | 890  |      | 915  | MHz        |

| Insertion loss                      |      |      | 0.5  | dB         |

| Coupling factor                     |      | 15   |      | dB         |

| Directivity                         | 13   |      | 14   | dB         |

| Impedance level of the main line    |      | 50   |      | ohm        |

| VSWR on main line                   |      |      | 1.6  |            |

| Impedance level of the coupled line |      | 50   |      | ohm        |

NMP part no. 4551001

#### **Power detector**

| Parameter                                                | Min. | Тур. | Max. | Unit/Notes |

|----------------------------------------------------------|------|------|------|------------|

| Supply voltage                                           | 2.7  | 2.8  | 2.85 | V          |

| Supply current                                           |      |      | 2.0  | mA         |

| Frequency range                                          | 890  |      | 915  | MHz        |

| Dynamic range                                            | 45   |      |      | dB         |

| Linear range, *                                          | 35   |      |      | dB         |

| Bias current for detector diode                          |      | 40   |      | uA         |

| Input power range, **                                    | -8   |      | 20   | dBm        |

| Output voltage                                           | 0.1  |      | 2.2  | V          |

| Variation of the detected voltage over temperature range |      |      | 0.7  | mV/°C      |

| Load resistance                                          | 10   |      |      | kohm       |

- \* RF input voltage versus detected output voltage

- \* \* Directional coupler coupling factor 14 dB

#### Power control section in SUMMA, closed loop characteristics

| Parameter               | Min. | Тур. | Max. | Unit/Notes |

|-------------------------|------|------|------|------------|

| Supply voltage          | 2.7  | 2.8  | 2.85 | V          |

| Supply current          |      | tbd. |      | mA         |

| TXP input voltage, LOW  |      |      | 0.5  | V          |

| TXP input voltage, HIGH | 2.4  |      |      | V          |

| Detector input voltage  | 0.1  |      | 2.2  | V          |

| TXC input voltage       | 0.1  |      | 2.2  | V          |

Page 3 – 26 Original 02/99

| Parameter                                           | Min.            | Тур. | Max. | Unit/Notes |

|-----------------------------------------------------|-----------------|------|------|------------|

| TXC and TXP input resistance                        | 50              |      |      | kohm       |

| TXC and TXP input capacitance                       |                 | 4    |      | pF         |

| Output voltage (POP & POG)                          | 0.5             |      | 2.2  | V          |

| POP- and POG-output impedance                       |                 | 50   |      | ohm        |

| POP and POG –output current driving capability      | +/- 4           |      |      | mA         |

| Switch on resistance (bet-<br>ween INL& POP or POG) |                 | tbd. |      | ohm        |

| Voltage of POP/POG when inactive (max. 3.5mA sink)  |                 | 0.1  |      | V          |

| Offset of OP1 and OP2 op.amp.                       | <del>-4</del> 0 |      | 40   | mV         |

| Temperature coefficient of the offset voltage       |                 | 30   |      | uV/deg.C   |

| Bandwidth ( OP1 & OP2 ), unity gain                 | 6               |      |      | MHz        |

| Open loop gain                                      |                 | 20   |      | dB         |

| Closed loop gain                                    |                 | 15   |      | dB         |

| Closed loop -3 dB bandwidth                         |                 | 70   |      | kHz        |

| Phase margin                                        | 45              | 60   |      | degrees    |

| Gain margin                                         |                 | 30   |      | dB         |

#### **Synthesizers blocks**

#### **VCTCXO**, reference oscillator

| Parameter                                                                                      | Min.  | Тур.    | Max   | Unit/.Notes |

|------------------------------------------------------------------------------------------------|-------|---------|-------|-------------|

| Supply voltage, Vcc                                                                            | 2.70  | 2.80    | 2.85  | V           |

| Current consumption, Icc                                                                       |       |         | 1.5   | mA          |

| Operating temperature range                                                                    | -20   |         | +75   | deg. C      |

| Nominal frequency                                                                              |       | 13      |       | MHz         |

| Output voltage swing<br>( swing of 13 MHz component, selective measurement from the spectrum ) | 800   |         |       | mVpp        |

| Load, resistance capacitance                                                                   |       | 2<br>10 |       | kohm<br>pF  |

| Frequency tolerance @+25 deg. C                                                                | - 1.0 |         | + 1.0 | ppm         |

| Frequency tolerance after reflow (@ +25 deg. C)                                                | -2.0  |         | + 2.0 | ppm         |

| Parameter                                                                                     | Min.   | Тур. | Max    | Unit/.Notes                                       |

|-----------------------------------------------------------------------------------------------|--------|------|--------|---------------------------------------------------|

| Frequency stability vs. temperature ( ref. @+25, -20+75 deg. C )                              | - 5.0  |      | + 5.0  | ppm                                               |

| Frequency stablity vs. supply voltage ( 2.8 V +/- 100 mV )                                    | - 0.1  |      | + 0.1  | ppm                                               |

| Frequency stability vs. load change ( 2 kohm//10 pF +/- 10 % )                                | - 0.3  |      | + 0.3  | ppm                                               |

| Aging                                                                                         | - 1.0  |      | + 1.0  | ppm/year                                          |

| Nominal control voltage, Vc                                                                   |        | 1.15 |        | V                                                 |

| Voltage control range                                                                         | 0.0    |      | 2.3    | V                                                 |

| Voltage control characteristics ( see note 1. )                                               | +/- 12 |      | +/- 24 | ppm/V when<br>0.3 V <vc<2.3 td="" v<=""></vc<2.3> |

| Vc input resistance                                                                           | 1      |      |        | Mohm                                              |

| Frequency adjustment                                                                          | 3.0    |      |        | ppm with inter–<br>nal trimmer                    |

| Harmonics ( with 2 kohm//10 pF )                                                              |        |      | - 5    | dBc                                               |

| Start up time output level within 90% output frequency limits +/-0.05ppm from the final value |        |      | 5<br>5 | ms                                                |

| Phase noise @ 1 kHz offset                                                                    |        |      | -130   | dBc/Hz                                            |

#### **VHF PLL in SUMMA**

The same VHF VCO and also the same frequency is used so the VHF PLL is common.

Table 2. VHF-synthesizer, specification

| Parameter                                                         | Min. | Тур. | Max.                     | Unit/Notes |

|-------------------------------------------------------------------|------|------|--------------------------|------------|

| Start up settling time                                            |      |      | 3.0                      | ms         |

| Phase error                                                       |      |      | 1                        | deg./rms   |

| Sidebands<br>+/- 1 MHz<br>+/- 2 MHz<br>+/- 3 MHz<br>> +/- 3.0 MHz |      |      | -70<br>-80<br>-80<br>-90 | dBc        |

Table 3. VHF PLL block in SUMMA, specification

| Parameter                 | Min. | Тур. | Max. | Unit/notes |

|---------------------------|------|------|------|------------|

| Input frequency range     | 150  |      | 500  | MHz        |

| Input signal level        | 80   |      | 800  | m∨pp       |

| Input resistance          | tbd. |      |      | kohm       |

| Input capacitance         |      |      | tbd. | pF         |

| Supply current            |      | 3.5  |      | mA         |

| Reference input frequency |      |      | 30   | MHz        |

Page 3 – 28 Original 02/99

Table 3. VHF PLL block in SUMMA, specification (continued)

| Parameter                                                | Min. | Тур.         | Max.   | Unit/notes |

|----------------------------------------------------------|------|--------------|--------|------------|

| Phase comparison frequency                               |      |              | 1      | MHz        |

| Charge pump output current 1 current 2                   |      | 0.5<br>2.0   |        | mA         |

| Sink to source current matching error of the charge pump |      |              | +/- 5  | %          |

| Charge pump current error                                |      |              | +/- 10 | %          |

| Charge pump min. output voltage                          |      | 0.5          |        | V          |

| Charge pump max. output voltage                          |      | *<br>Vcp–0.5 |        | V          |

| Charge pump leakage current                              |      |              | 5      | nA         |

| Phase detector phase noise level                         |      |              | -163   | dBc/Hz     |

<sup>\*</sup>Vcp = 5V

#### VHF VCO and low pass filter

| Parameter                                                            | Min. | Тур. | Max.                 | Unit/Notes                                  |

|----------------------------------------------------------------------|------|------|----------------------|---------------------------------------------|

| Supply voltage range                                                 | 2.7  | 2.8  | 2.85                 | V                                           |

| Current consumption                                                  |      | 4    | 7                    | mA                                          |

| Control voltage                                                      | 0.5  |      | 4.0                  | V                                           |

| Operation frequency                                                  |      | 232  |                      | MHz                                         |

| Output level                                                         | -13  | -10  |                      | dBm ( output after the lowpass filter )     |

| Harmonics                                                            |      |      | -30                  | dBc, ( filtered )                           |

| Phase noise,<br>fo +/- 600 kHz<br>fo +/- 1600 kHz<br>fo +/- 3000 kHz |      |      | -120<br>-130<br>-140 | dBc                                         |

| Control voltage sensitivity                                          | 8.0  |      | 14.0                 | MHz/V                                       |

| Pushing figure                                                       |      |      | +/- 2                | MHz/V                                       |

| Frequency stability                                                  |      |      | +/- 3                | MHz ( over temperature range –10+75 C deg.) |

| Spurious content                                                     |      |      | -70                  | dBc                                         |

**Technical Documentation**

#### **UHF PLL**

Table 4. UHF-synthesizer,

| Parameter                                                                                            | Min. | Тур. | Max.                            | Unit/Notes                                  |

|------------------------------------------------------------------------------------------------------|------|------|---------------------------------|---------------------------------------------|

| Start up settling time                                                                               |      |      | 3.0                             | ms                                          |

| Settling time +/- 25 MHz                                                                             |      | 500  | 800                             | us, ( into +/– 20 Hz from final frequency ) |

| Phase error                                                                                          |      |      | 3.7                             | deg./rms                                    |

| Sidebands<br>+/- 200 kHz<br>+/- 400 kHz<br>+/- 600+/-1400 kHz<br>+/-1.4 +/- 3.0 MHz<br>> +/- 3.0 MHz |      |      | -40<br>-60<br>-66<br>-76<br>-86 | dBc                                         |

Table 5. UHF PLL block in SUMMA

| Parameter                                                | Min. | Тур.       | Max.   | Unit/notes |

|----------------------------------------------------------|------|------------|--------|------------|

| Input frequency range                                    | 650  |            | 1700   | MHz        |

| Input signal level (f<1.5 GHz)                           | 200  |            |        | mVpp       |

| Input resistance                                         | tbd. |            |        | kohm       |

| Input capacitance                                        |      |            | tbd.   | pF         |

| Supply current                                           |      | 8          |        | mA         |

| Reference input frequency                                |      |            | 30     | MHz        |

| Reference input level                                    | 100  |            |        | mVpp       |

| Reference input impedance                                |      | tbd.       |        |            |

| Phase comparison frequency                               |      |            | 1      | MHz        |

| Charge pump output current 1 current 2                   |      | 0.5<br>2.0 |        | mA         |

| Sink to source current matching error of the charge pump |      |            | +/- 5  | %          |

| Charge pump current error                                |      |            | +/- 10 | %          |

| Charge pump current temperature variation                |      |            | tbd.   | %          |

| Charge pump leakage current                              |      |            | 5      | nA         |

| Phase detector phase noise level                         |      |            | -163   | dBc/Hz     |

#### **UHF VCO module**

| Parameter           | Conditions                 | Rating      | Unit/<br>Notes |

|---------------------|----------------------------|-------------|----------------|

| Supply voltage, Vcc |                            | 2.8 +/- 0.1 | V              |

| Supply current, Icc | Vcc = 2.8 V,<br>Vc= 2.25 V | < 10        | mA             |

| Control voltage, Vc | Vcc = 2.8 V                | 0.8 3.7     | V              |

Page 3 – 30 Original 02/99

| Parameter                                                                          | Conditions                              | Rating                       | Unit/<br>Notes |

|------------------------------------------------------------------------------------|-----------------------------------------|------------------------------|----------------|

| Oscillation frequency                                                              | Vcc = 2.8 V<br>Vc = 0.8 V<br>Vc = 3.7 V | < 1006<br>> 1031             | MHz<br>MHz     |

| Tuning voltage in center frequency                                                 | f = 1018.5 MHz                          | 2.25 +/- 0.25                | V              |

| Tuning voltage sensitivity in operating frequency range on each spot freq.         | Vcc = 2.8 V<br>f=10061031<br>MHz        | 14 +/- 2                     | MHz/V          |

| Output power level                                                                 | Vcc=2.7 V<br>f=10061031<br>MHz          | –6.0 min.                    | dBm            |

| Output impedance and VSWR                                                          | f=10061031<br>MHz                       | 50 ohms,VSWR <2              |                |

| Phase noise, fo +/- 25 kHz<br>fo +/- 600 kHz<br>fo +/- 1600 kHz<br>fo +/- 3000 kHz | Vcc=2.8 V<br>f=10061031<br>MHz          | -100<br>-120<br>-130<br>-140 | dBc/Hz<br>max. |

| Pulling figure                                                                     | VSWR=2, any phase                       | +/- 1.0                      | MHz<br>max.    |

| Pushing figure                                                                     | Vcc=2.8 +/- 0.1                         | +/- 2.0                      | MHz/V<br>max.  |

| Frequency stability over temperature range                                         | Ta=-20 +75<br>deg. C                    | +/- 3.0                      | MHz<br>max.    |

| Harmonics                                                                          |                                         | –10 max.                     | dBc            |

| Spurious                                                                           | Vcc=2.8 V,<br>Vc=06 V                   | –70 max.                     | dBc            |

| Input capacitance in Vc-pin                                                        | Vc= 0 V                                 | 100 max.                     | pF             |

#### UHF local signal input in CRFU\_1a

| Parameter             | Min. | Тур. | Max. | Unit/Notes |

|-----------------------|------|------|------|------------|

| Input frequency range | 990  |      | 1040 | MHz        |

| Input level           | 200  |      | 700  | mVpp       |

| Input resistance      |      | 100  |      | ohm        |

| Input capacitance     |      |      | 1.5  | pF         |

#### **RF/BB/DSP Interface**

The following three sections describe the hardware and timing interface between RF and the BB/DSP section of the RAE–2.

#### **Interface Signal Characteristics**

The interface signals between the BB and the RF section are shown in the next table as a logical interface. On physical board level baseband supplies voltages from CCONT to separate RF sub-blocks. The maximum values specified for the digital signals in the table are the absolute maximum values from the RF interface point of view.

Table 6. AC and DC Characteristics of RF/BB signals

| Signal name | From - To    | Function                                                              |

|-------------|--------------|-----------------------------------------------------------------------|

| VBATT       | Battery RF   | Supply voltage for RF<br>(PA on/PA off)                               |

| VXOENA      | MAD CCONT    | VR1, VR6 in CCONT ON                                                  |

|             |              | VR1, VR6 in CCONT<br>OFF                                              |

| SYNPWR      | MAD CCONT    | VR3, VR4 in CCONT ON                                                  |

|             |              | VR3,VR4 in CCONT OFF                                                  |

| RXPWR       | MAD CCONT    | VR2, VR5 in CCONT ON                                                  |

|             |              | VR2, VR5 in CCONT OFF                                                 |

| TXPWR       | MAD CCONT    | VR7 in CCONT ON                                                       |

|             |              | VR7 in CCONT OFF                                                      |

| VREF        | CCONT SUMMA  | Reference voltage for SUMMA and CRFU1a                                |

| PDATA0      | MAD CRFU1A   | Nominal gain in LNA                                                   |

|             |              | Reduced gain in LNA                                                   |

| SENA        | MAD SUMMA    | PLL enable                                                            |

| SDATA       | MAD SUMMA    | Synthesizer data                                                      |

| SCLK        | MAD SUMMA    | Synthesizer clock                                                     |

| AFC         | COBBA VCTCXO | Automatic frequency control signal for VC(TC)XO                       |

|             |              | 1010000Hz                                                             |

| RFC         | VCTCXO MAD   | High stability clock signal for the logic circuits                    |

| RXIP/RXIN   | SUMMA COBBA  | Differential RX 13 MHz signal to baseband                             |

| TXIP/TXIN   | COBBA SUMMA  | Differential in–phase TX baseband signal for the RF modulator         |

| TXQP/TXQN   | COBBA SUMMA  | Differential quadrature phase TX baseband signal for the RF modulator |

| TXP         | MAD SUMMA    | Transmitter power control enable                                      |

Page 3 – 32 Original 02/99

Table 6. AC and DC Characteristics of RF/BB signals (continued)

| Signal name | From - To   | Function                  |  |  |

|-------------|-------------|---------------------------|--|--|

| TXC         | COBBA SUMMA | Transmitter power control |  |  |

|             |             | 0200 kHz                  |  |  |

| RXC         | COBBA SUMMA | Receiver gain control     |  |  |

|             |             | 0200 kHz                  |  |  |

TXC and AGC signals originate from the same DAC, controlled in COBBA

#### **Data Interface and Timing**

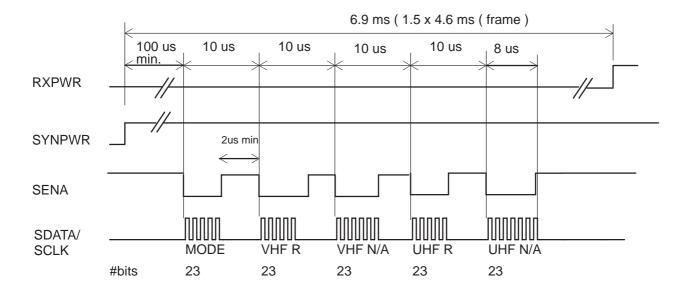

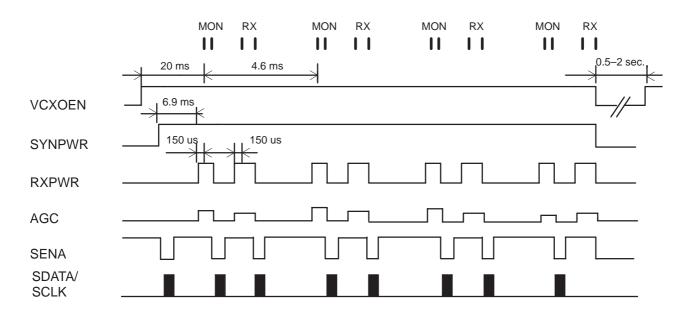

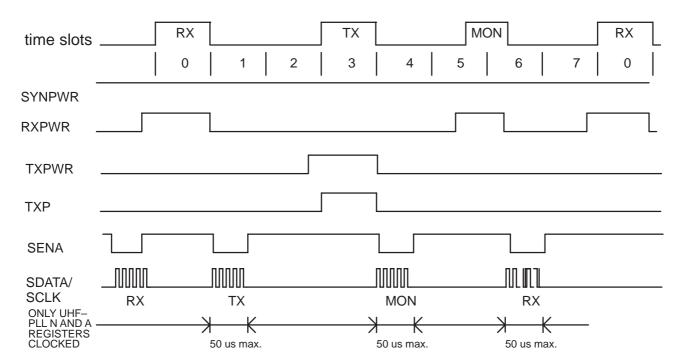

The SUMMA is programmed via the serial bus SENA, SDATA and SCLK. The data of the SDATA is clocked by rising edge of SCLK. The data is fed MSB first and address bits before data bits. The data for the Programmable dual modulus counter is fed first and the Swallow counter last. SENA is kept low while clocking the data. (Figure below)

During programming, the charge pump attached to programmed divider is switched to high impedance state. Also all counters connected to the PLL that is programmed, are kept on reset while the SENA is low.

Table 7. Logic levels

| Parameters | Min | Тур | Max | Units |

|------------|-----|-----|-----|-------|

| High       | 2   |     |     | Volt  |

| Low        |     |     | 0.8 | Volt  |

PAMS

BS8\_RF Technical Documentation

Figure 3. Synthesizer timing / IDLE, one monitoring/frame, frame can start also from RX-burst

Figure 4. UHF-synthesizer timing/clocking on traffic channel

Page 3 – 34 Original 02/99

#### **Transmit Power Timing**

Figure 5. Transmitter timing diagram for normal bursts

**Technical Documentation**